Chapter1. The Devices: Diode and MOS Transistors (Chapter 3 in textbook)

[Adapted from Rabaey's Digital Integrated Circuits, ©2002, J. Rabaey et al.]

#### © Digital Integrated Circuits<sup>2nd</sup>

Devices

Devices

# Goal of this chapter

- Present intuitive understanding of device operation

- Introduction of basic device equations

- Introduction of models for manual analysis

- Introduction of models for SPICE simulation

- Analysis of secondary and deep-submicron effects

- □ Future trends

Devices

#### **Semiconductors**

© Digital Integrated Circuits<sup>2nd</sup>

- Semiconductor: electrical conductivity greater than insulator, but less than conductor.

- Derived Semiconductor materials: Si, Ge, GaAs, etc.

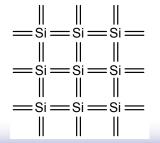

- □ Transistors are built on a silicon (Si) substrate

- □ Silicon is a Group IV semiconductor material

- □ Forms crystal lattice with bonds to four neighbors

#### Silicon Material

© Digital Integrated Circuits<sup>2nd</sup>

- Pure silicon: very few free carriers, conducts poorly

- □ Intrinsic Si (undoped):

- $n=p=n_i=1.5\times 10^{10}/\text{cm}^3$  (room temperature) where *n* (p): free-electron(hole) concentration,  $n_i$ : intrinsic carrier concentration.

- Adding dopants increases the conductivity

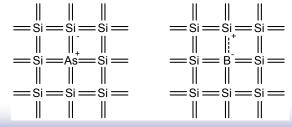

- ✓ Group V dopants: contribute extra electron (n-type)

- ✓ Group III dopants: contribute hole (missing electron, p-type)

© Digital Integrated Circuits<sup>2nd</sup>

#### **Dopants**

- Donor: impurity with valence ≥5 (e.g. P, As) => n-type with free electrons. Assume doping concentration of donor as N<sub>D</sub>.

Assume the provide the provided of the pr

- 1). Concentration of free electrons in n-type material ( $n_n$ ):  $n_n = N_D >> n_i$

- 2). Concentration of free holes in n-type material (p\_n)  $p_n = n_i^2 / N_D$

- □ Acceptor: impurity with valence  $\leq$ 3 (e.g. B) => p-type with free holes. Assume doping concentration of acceptor as N<sub>A</sub>.

- 1). Concentration of free holes in p-type material ( $p_p$ ):  $p_p=N_A>>n_i$

- 2). Concentration of free electrons in p-type material (n<sub>p</sub>)  $n_p = n_i^2/N_A$

# © Digital Integrated Circuits<sup>2nd</sup> Devices © Digital Integrated Circuits<sup>2nd</sup> Bulk

# The Diode

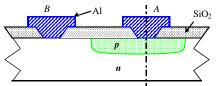

Cross-section of *pn*-junction in an IC process

#### Mostly occurring as parasitic element in Digital ICs

Devices

# **Depletion Region**

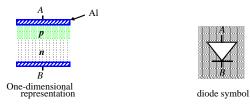

*p-n Junctions*

diode.

SiO

direction

□ A junction between p-type and

Current flows only in one

Anode

$p^+$

n

n-type semiconductor forms a

#### © Digital Integrated Circuits<sup>2nd</sup>

n-type

cathode

Anode

Ż

Cathode

p-type

anode

Cathode

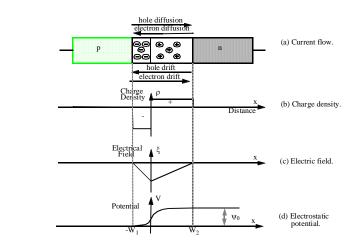

#### **PN Junction**

© Digital Integrated Circuits<sup>2nd</sup>

□ Built-in potential of PN junction:  $\Phi_0 = V_T \ln\left(\frac{N_A N_D}{n_i^2}\right)$ where the thermal voltage V<sub>T</sub>: V<sub>T</sub>=kT/q, in it, k: Boltzmann constant, k=1.38×10<sup>-23</sup> m<sup>2</sup>·kg·s<sup>-2</sup>·K<sup>-1</sup>, q: electron charge, q=1.6×10<sup>-19</sup>C. At room temperature (T=300K), V<sub>T</sub>=0.026V.

#### Reversed-biased Diode: Depletion Width Depletion Width depletion regi use Poisson's equation & charge neutrality ptype \_n-type - W = $x_p + x_n$ NA $2\varepsilon(\Psi_0+V_R)N_D$ $2\varepsilon(\Psi_0 + V_R)N_A$ $qN_A(N_D + N_A)$ $qN_D(N_D + N_A)$ • where V<sub>R</sub> is applied reverse bias ε is the permittivity of Si $W = \left[\frac{2\varepsilon(\Psi_0 + V_R)}{q}\frac{N_D + N_A}{N_D N_A}\right]$ ε = 1.04x10<sup>-12</sup> F/cm $\epsilon = K_{S}\epsilon_{0}$ , where $\epsilon_{0} = 8.85 \times 10^{-14}$ F/cm and $K_s = 11.8$ is the relative permittivity of silicon One-sided Step Junction $2\varepsilon(\Psi_0 + V_R)$ - if NA>>N (p+n diode) $W \cong x_n =$ most of junction on n-side $\int 2\varepsilon (\Psi_0 + V_R)$ - if $N_{\rm D} >> N_{\rm A}$ (n+p diode) • most of junction on p-side $W \cong x_p =$ © Digital Integrated Circuits<sup>2nd</sup> Devices

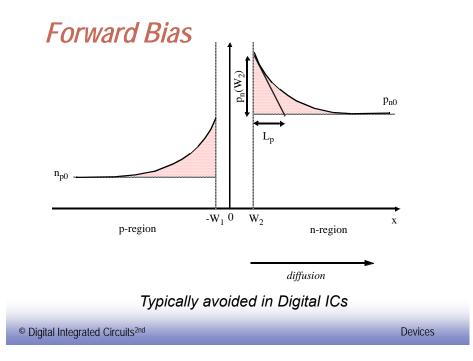

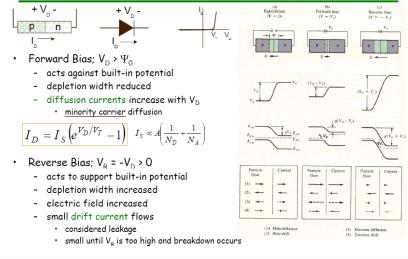

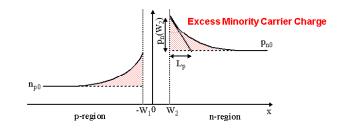

#### Forward-biased Junction

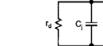

$\frac{1}{r_{d}} = \frac{dI_{D}}{dV_{D}} = I_{S} \frac{e^{V_{D}/V_{T}}}{V_{T}} = \frac{I_{D}}{V_{T}}$

- Drift current: current flow due to concentration gradient of the minority charge near junction

- □ Forward-bias current under forward-bias voltage V<sub>D</sub>:

$$\boxed{I_D = I_S \left( e^{V_D/V_T} - 1 \right)} \quad I_S \propto A \left( \frac{1}{N_D} + \frac{1}{N_D} \right)$$

Small-signal model of forward-biased diode 1). Incremental resistance r<sub>d</sub>

- 2). Depletion capacitance C<sub>i</sub>: for depletion width change and immobile charge change in depletion region.

- 3). Diffusion capacitance  $C_d$ : for minority carrier  $C_d = \frac{\tau_T}{r_d}$ concentration change close to junction. <sup>τ</sup>τ: transition time of diode (specified for a given technology)

© Digital Integrated Circuits<sup>2nd</sup>

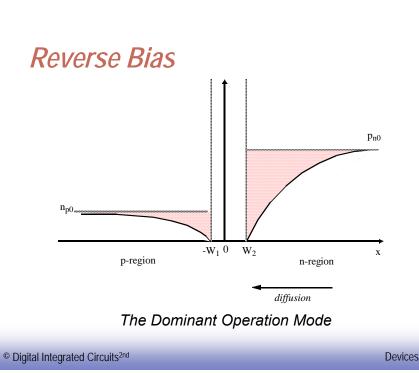

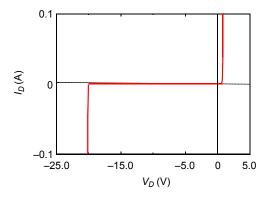

#### Reverse Bias Diode

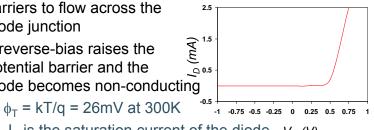

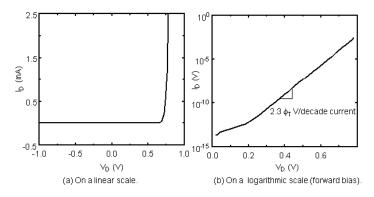

□ The *ideal diode equation* (for both forward and reversebias conditions) is:  $I_{D} = I_{s}(e^{V_{D}/\phi_{T}} - 1)$

where  $V_{D}$  is the voltage applied to the junction -

- a forward-bias lowers the potential barrier allowing carriers to flow across the diode junction

- a reverse-bias raises the potential barrier and the diode becomes non-conducting

Devices

$I_{\rm S}$  is the saturation current of the diode  $V_{\rm D}(V)$

```

© Digital Integrated Circuits<sup>2nd</sup>

```

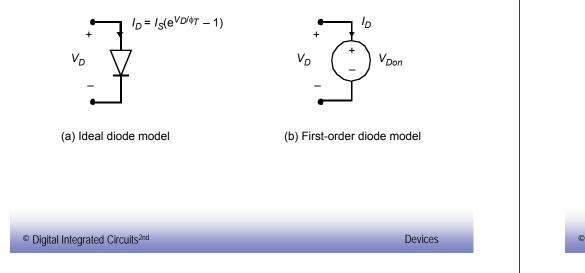

# Diode Current

$I_D = I_S \left( e^{V_D / \phi_T} - 1 \right)$

#### © Digital Integrated Circuits<sup>2nd</sup>

#### Models for Manual Analysis

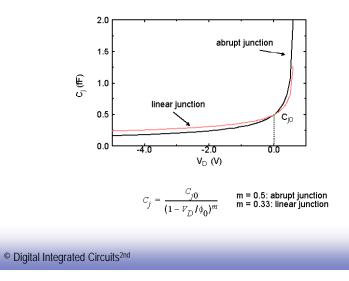

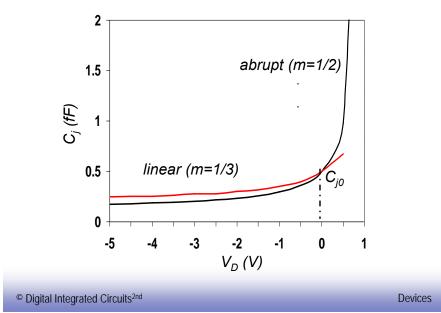

# Junction Capacitance

#### Junction Depletion Capacitance

- Depletion capacitance: capacitance due to varying charge storage in depletion regions.

- Reason: bias voltage changes =>junction widths change =>charge in depletion region changes => capacitance effect.

- Depletion capacitance:

$$\mathbf{C}_{j} = \frac{d\mathbf{Q}^{*}}{d\mathbf{V}_{\mathsf{R}}} = \left[\frac{q\mathbf{K}_{s}\varepsilon_{0}}{2(\Phi_{0} + \mathbf{V}_{\mathsf{R}})}\frac{\mathbf{N}_{\mathsf{A}}\mathbf{N}_{\mathsf{D}}}{\mathbf{N}_{\mathsf{A}} + \mathbf{N}_{\mathsf{D}}}\right]^{1/2} = \frac{\mathbf{C}_{j0}}{\sqrt{1 + \frac{\mathbf{V}_{\mathsf{R}}}{\Phi_{0}}}} \quad \mathbf{C}_{j0} = \sqrt{\frac{q\mathbf{K}_{s}\varepsilon_{0}}{2\Phi_{0}}}\frac{\mathbf{N}_{\mathsf{A}}\mathbf{N}_{\mathsf{D}}}{\mathbf{N}_{\mathsf{A}} + \mathbf{N}_{\mathsf{D}}}}$$

$C_{j0}$ : depletion capacitance per unit area at  $V_R$ =0. If  $N_A$ >> $N_D$  (one-side diode):

$$\mathbf{C}_{j} = \left[\frac{\mathbf{q}\mathbf{K}_{s}\varepsilon_{0}\mathbf{N}_{D}}{2(\Phi_{0} + \mathbf{V}_{R})}\right]^{1/2} = \frac{\mathbf{C}_{j0}}{\sqrt{1 + \frac{\mathbf{V}_{R}}{\Phi_{0}}}} \quad \text{where} \quad \mathbf{C}_{j0} = \sqrt{\frac{\mathbf{q}\mathbf{K}_{s}\varepsilon_{0}\mathbf{N}_{D}}{2\Phi_{0}}}$$

© Digital Integrated Circuits<sup>2nd</sup>

Devices

# **Diffusion Capacitance**

$$C_{d} = \frac{\mathrm{d}Q_{D}}{\mathrm{d}V_{D}} = \tau_{T} \frac{\mathrm{d}I_{D}}{\mathrm{d}V_{D}} \approx \frac{\tau_{T}I_{D}}{\phi_{T}}$$

© Digital Integrated Circuits<sup>2nd</sup>

# Secondary Effects

.

Avalanche Breakdown

|--|

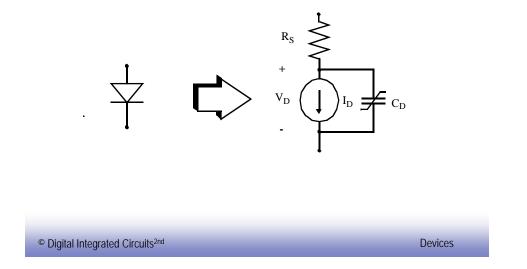

# Diode Model

#### **SPICE** Parameters

| Parameter Name                    | Symbol      | SPICE<br>Name | Units | Default<br>Value |

|-----------------------------------|-------------|---------------|-------|------------------|

| Saturation current                | $I_S$       | IS            | А     | 1.0 E-14         |

| Emission coefficient              | п           | N             | -     | 1                |

| Series resistance                 | $R_S$       | RS            | Ω     | 0                |

| Transit time                      | $\tau_T$    | TT            | sec   | 0                |

| Zero-bias junction<br>capacitance | $C_{j0}$    | C10           | F     | 0                |

| Grading coefficient               | т           | М             | -     | 0.5              |

| Junction potential                | <b>\$</b> 0 | VJ            | v     | 1                |

First Order SPICE diode model parameters.

# Device: The MOS Transistor

#### Device: The MOS Transistor

# What is a Transistor?

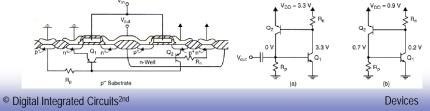

#### **Power Supply Voltage for CMOS**

- GND = 0 V

- In 1980's, V<sub>DD</sub> = 5V

- V<sub>DD</sub> has decreased in modern processes

High V<sub>DD</sub> would damage modern tiny transistors

Lower V<sub>DD</sub> saves power

- V<sub>DD</sub> = 3.3V, 2.5V, 1.8V, 1.5V, 1.2V, 1.0V, ...

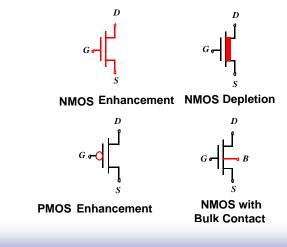

# *MOS Transistors -Types and Symbols*

#### © Digital Integrated Circuits<sup>2nd</sup>

####

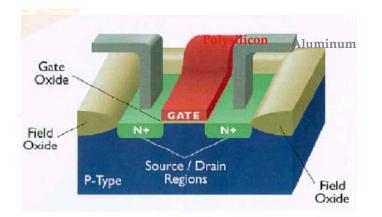

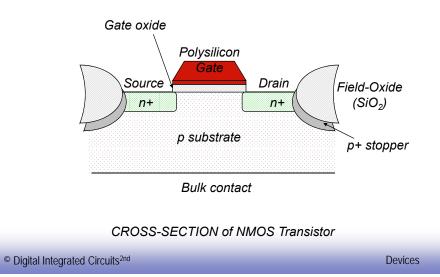

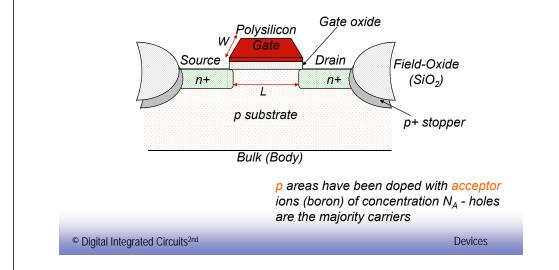

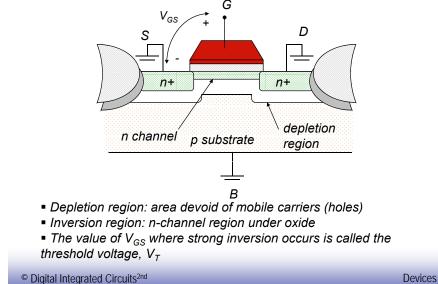

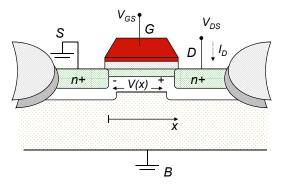

#### The NMOS Transistor Cross Section

*n* areas have been doped with donor ions (arsenic) of concentration  $N_D$  - electrons are the majority carriers

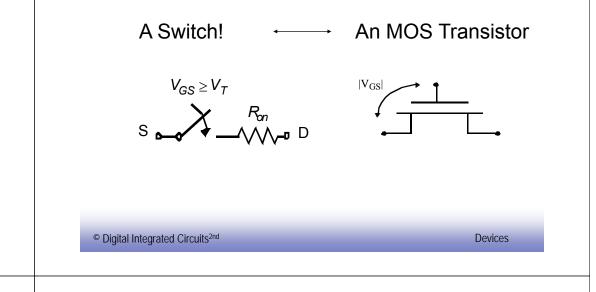

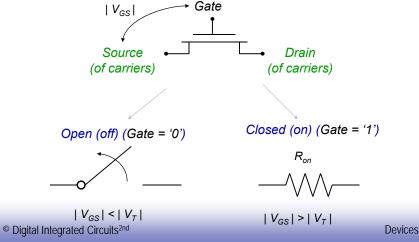

# Switch Model of NMOS Transistor

- We can view MOS transistors as electrically controlled switches

- Voltage at gate controls path from source to drain

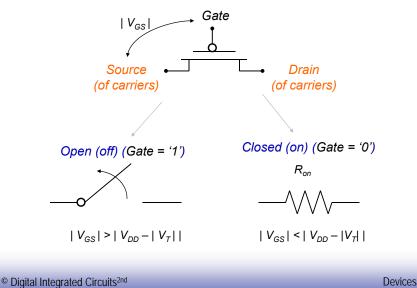

# Switch Model of PMOS Transistor

# Threshold Voltage Concept

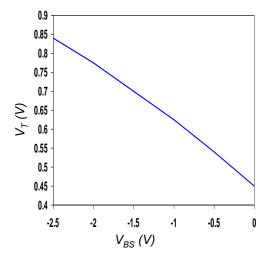

# The Threshold Voltage

where

$V_{T} = V_{T0} + \gamma(\sqrt{|-2\phi_{F} + V_{SB}|} - \sqrt{|-2\phi_{F}|})$

- $V_{T0}$  is the threshold voltage at  $V_{SB}$  = 0 and is mostly a function of the manufacturing process

- Difference in work-function between gate and substrate material, oxide thickness, Fermi voltage, charge of impurities trapped at the surface, dosage of implanted ions, etc.

- $V_{SB}$  is the source-bulk voltage

- $\phi_F = -\phi_T ln(N_A/n_i)$  is the Fermi potential ( $\phi_T = kT/q = 26mV$  at 300K is the thermal voltage;  $N_A$  is the acceptor ion concentration;  $n_i \approx 1.5 \times 10^{10}$  cm<sup>-3</sup> at 300K is the intrinsic carrier concentration in pure silicon)

- $\gamma = \sqrt{(2q_{\mathcal{E}_{si}}N_A)/C_{ox}}$  is the body-effect coefficient (impact of changes in  $V_{SB}$ ) ( $\varepsilon_{si}$ =1.053x10<sup>-10</sup>F/m is the permittivity of silicon;  $C_{ox} = \varepsilon_{ox}/t_{ox}$  is the gate oxide capacitance with  $\varepsilon_{ox}$ =3.5x10<sup>-11</sup>F/m)

# The Body Effect

• V<sub>SB</sub> is the substrate bias voltage (normally positive for n-channel devices with the body tied to ground)

• A negative bias causes  $V_T$  to increase from 0.45V to 0.85V

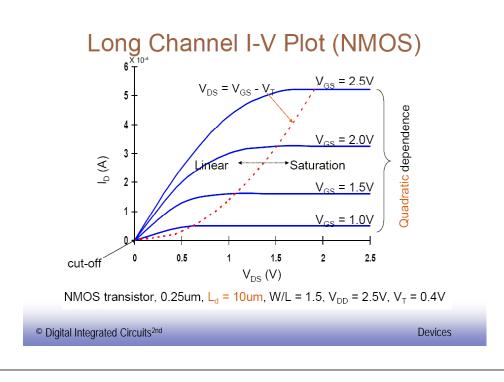

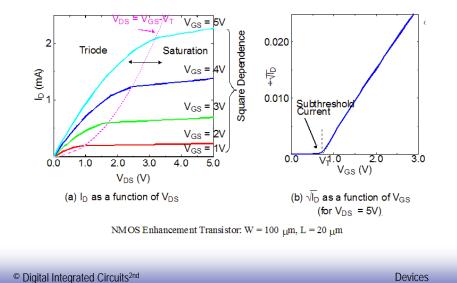

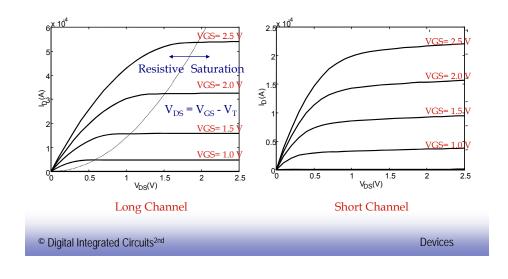

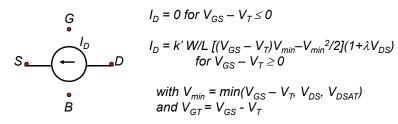

#### Long Channel I-V Relation (NMOS)

#### **MOSFET** Operating Regions

- Strong inversion when  $V_{GS} > V_T$

- Linear (resistive) when  $\rm V_{\rm DS}$  <  $\rm V_{\rm DS-sat}$

- Saturated (constant current) when  $V_{DS} \ge V_{DS-sat}$

- Weak inversion (sub-threshold) when  $V_{GS} \leq V_{T}$

- Exponential in  $V_{\text{GS}}$  with linear  $V_{\text{DS}}$  dependence

- $V_{DS-sat}$ : Drain-source voltage when the channel becomes pinched off.  $V_{DS-sat} = V_{GS} V_T$

- Transconductance

- process transconductance,  $k'_n = \mu_n Cox$  (for NMOS),  $k'_p = \mu_p Cox$  (for PMOS). • constant for a given fabrication process

- device transconductance,  $\beta_n = k'_n W/L$  (for NMOS),  $\beta_p = k'_p W/L$  (for PMOS).

Devices

#### Transistor in Linear Mode Assuming $V_{GS} > V_T$

□ When  $V_{GS}$ > $V_{T}$ , and  $V_{DS}$ < $V_{GS}$ - $V_{T}$ , a current flows from drain to source □ The current is a linear function of both  $V_{GS}$  and  $V_{DS}$

#### Voltage-Current Relation: Linear Mode

For long-channel devices (L > 0.25 micron)

$\Box \text{ When } V_{\text{DS}} \leq V_{\text{GS}} - V_{\text{T}}$

$I_{\rm D} = k'_{\rm n} W/L [(V_{\rm GS} - V_{\rm T})V_{\rm DS} - V_{\rm DS}^2/2]$

where

$k'_n = \mu_n C_{ox} = \mu_n \varepsilon_{ox} / t_{ox}$  = is the process transconductance parameter ( $\mu_n$  is the carrier mobility (m<sup>2</sup>/Vsec))

$k_n = k'_n$  W/L is the gain factor of the device

For small  $V_{DS}$ , there is a linear dependence between  $V_{DS}$  and  $I_D$ , hence the name resistive or linear region

© Digital Integrated Circuits<sup>2nd</sup>

Devices

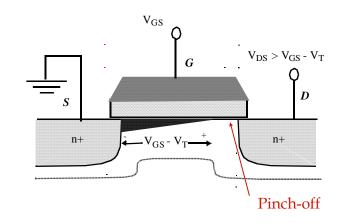

# Transistor in Saturation Mode Vos Vos Image: Second Sec

- Increasing V<sub>DS</sub> beyond V<sub>GS</sub>-V<sub>T</sub> causes the depletion region at drain to grow  $\rightarrow$  effective channel length L decreases

- Since ID is inversely proportional to L, as L decreases, ID increases, but compared to linear mode, it is relatively constant

© Digital Integrated Circuits<sup>2nd</sup>

#### *Voltage-Current Relation: Saturation Mode* For long channel devices

$\Box \text{ When } V_{\text{DS}} \geq V_{\text{GS}} - V_{\text{T}}$

$I_{\rm D}' = k'_{\rm n}/2 \text{ W/L} [(V_{\rm GS} - V_{\rm T})^2]$

- since the voltage difference over the induced channel (from the pinch-off point to the source) remains fixed at  $V_{GS} V_T$

- However, the effective length of the conductive channel is modulated by the applied V<sub>DS</sub>, so

$$I_{\rm D} = I_{\rm D}' (1 + \lambda V_{\rm DS})$$

where  $\lambda$  is the channel-length modulation (varies with the inverse of the channel length)

# Transistor in Saturation

#### Current-Voltage Relations

$$\begin{aligned}

G & \longrightarrow D \\

I_{S} & V_{T} = V_{T0} + \gamma(\sqrt{|-2\phi_{F} + V_{SB}|} - \sqrt{|-2\phi_{F}|}) \\

V_{DS-sat} = V_{GS} - V_{T} = V_{eff}

\end{aligned}$$

1). Linear (Triode) Region:  $V_{GS} > V_{T}, V_{DS} \leq V_{GS} - V_{T}$

$$I_{D} = k_{n} \frac{W}{L} [(V_{GS} - V_{T})V_{DS} - \frac{V_{DS}^{2}}{2}] \\

with \quad k_{n}' = \mu_{n}C_{ox} = \frac{\mu_{n}\delta_{ox}}{t_{ox}} \Rightarrow \text{Process Transconductance} \\

Parameter

\end{aligned}$$

2). Saturation (Active) Region:  $V_{GS} > V_{T}, V_{DS} \geq V_{GS} - V_{T}$

$$I_{D} = \frac{k_{n}W}{2L} (V_{GS} - V_{T})^{2} [1 + \lambda(V_{DS})] \\

Shub-threshold (Cutoff) Region:  $V_{GS} \leq V_{T} \\

I_{D} = 0 \\

al Integrated Circuits^{2nd}$$$

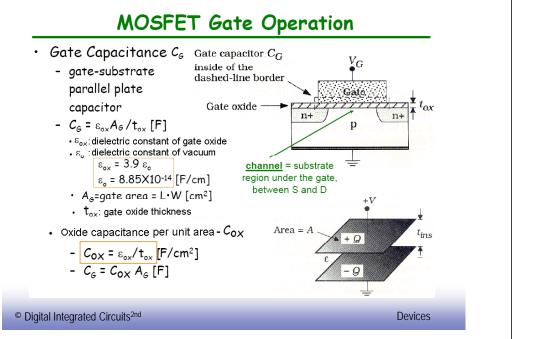

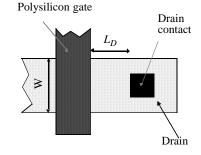

#### **Current Determinates**

For a fixed V<sub>DS</sub> and V<sub>GS</sub> (> V<sub>T</sub>), I<sub>DS</sub> is a function of

- the distance between the source and drain L

- the channel width W

- the threshold voltage V<sub>T</sub>

- the thickness of the SiO<sub>2</sub> t<sub>ox</sub>

- the dielectric of the gate insulator  $(SiO_2) \epsilon_{ox}$

- the carrier mobility

© Digital Integrated Circuits<sup>2nd</sup>

- for nfets:  $\mu_n = 500 \text{ cm}^2/\text{V-sec}$

- for pfets:  $\mu_p$  = 180 cm<sup>2</sup>/V-sec

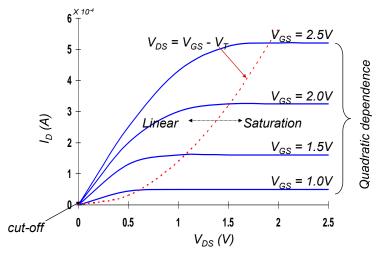

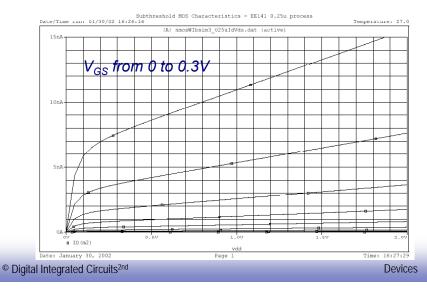

# Long Channel I-V Plot (NMOS)

NMOS transistor, 0.25 $\mu$ ,  $L_d$  = 10 $\mu$ , W/L = 1.5,  $V_{DD}$  = 2.5V,  $V_T$  = 0.4V

# Second Order Effects Channel Length Modulation Square Law Equation predicts I<sub>D</sub> is constant with V<sub>DS</sub> However, I<sub>D</sub> actually increases slightly with V<sub>DS</sub>

- + due to effective channel getting shorter as  $V_{\mbox{\scriptsize DS}}$  increases

- effect called channel length modulation

- Channel Length Modulation factor,  $\boldsymbol{\lambda}$

- + models change in channel length with  $V_{\mbox{\tiny DS}}$

- Corrected  $\mathbf{I}_{\mathsf{D}}$  equation

$$I_D = \frac{\mu_n C_{OX}}{2} \frac{W}{L} (V_{GS} - V_t)^2 \left(1 + \lambda (V_{DS} - V_{eff})\right)$$

- so far we have assumed that substrate and source are grounded

- if source not at ground, source-to-bulk voltage exists,  $V_{\text{SB}}$  > 0

- $V_{SB}$  > 0 will increase the threshold voltage, Vtn =  $f(V_{SB})$

- called Body Effect, or Body-Bias Effect

© Diai

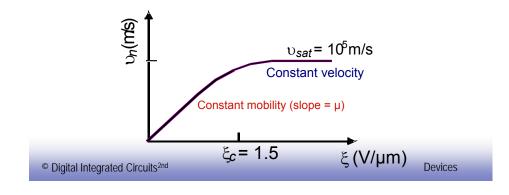

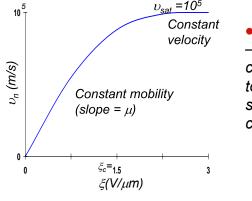

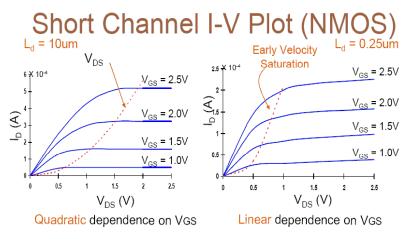

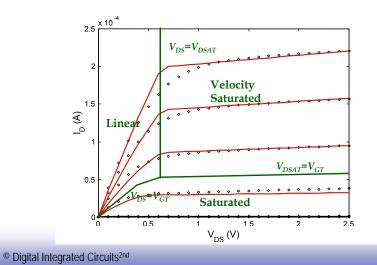

# Velocity Saturation

For long channel device: carrier velocity increases linearly with E-field: ν<sub>n</sub>=-μ<sub>n</sub>ξ(x)=μ<sub>n</sub>(dV/dx)

• For transistors with very short channel length (short-channel devices), when E-field along the channel reaches a critical value  $\xi_c$ , the velocity of carriers saturates due to scattering effects (collisions suffered by carriers).

# Velocity Saturation Effects

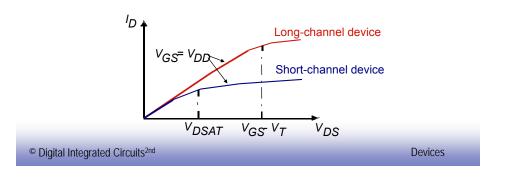

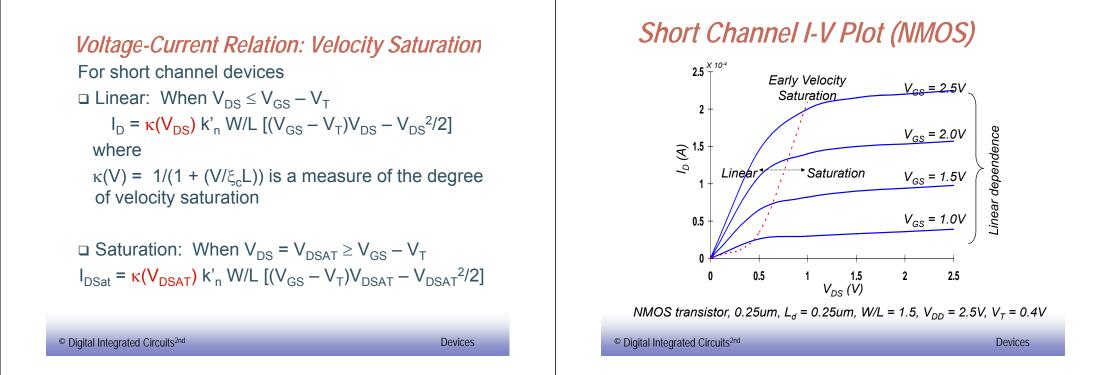

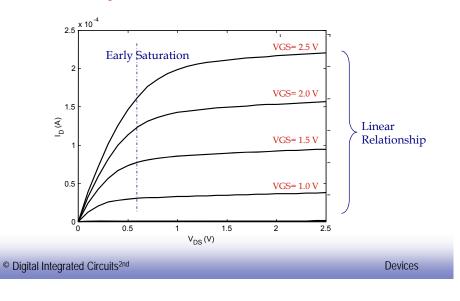

For short channel devices and large enough  $V_{\rm GS}-V_{\rm T}$

•  $V_{DSAT} < V_{GS} - V_T so$ the device enters saturation before  $V_{DS}$ reaches  $V_{GS} - V_T$  and operates more often in saturation

• *I*<sub>DSAT</sub> has a linear dependence wrt V<sub>GS</sub> so a reduced amount of current is delivered for a given control voltage

#### Devices

#### Perspective

• For short channel transistor, due to velocity saturation:

✓ Transistor enters saturation before  $V_{DS}$  reaches  $V_{GS}$ - $V_T$ . Short-channel devices experience extended saturation region, and tend to operation more often in saturation conditions.

✓ Saturation current  $I_{DSAT}$  shows linear dependence to  $V_{GS}$  instead of squared dependence in long-channel device. This reduces the amount of current a transistor can deliver for a given control voltage.

# Short Channel Effects

• Behavior of short channel device mainly due to

• Velocity saturation – the velocity of the carriers saturates due to scattering (collisions suffered by the carriers)

• For an NMOS device with L of .25µm, only a couple of volts difference between D and S are needed to reach velocity saturation

© Digital Integrated Circuits<sup>2nd</sup>

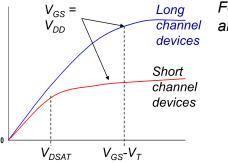

## *Current-Voltage Relations The Deep-Submicron Era*

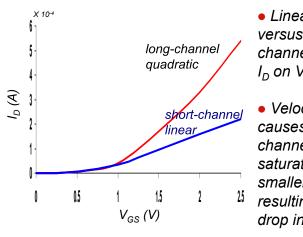

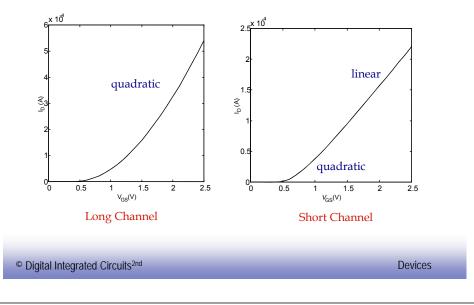

#### MOS I<sub>D</sub>-V<sub>GS</sub> Characteristics

• Linear (short-channel) versus quadratic (longchannel) dependence of I<sub>D</sub> on V<sub>GS</sub> in saturation

• Velocity-saturation causes the shortchannel device to saturate at substantially smaller values of V<sub>DS</sub> resulting in a substantial drop in current drive

(for  $V_{DS}$  = 2.5V, W/L = 1.5)

© Digital Integrated Circuits<sup>2nd</sup>

# I<sub>D</sub> versus V<sub>GS</sub>

# $I_D$ versus $V_{DS}$

• I<sub>DSAT</sub> has a linear dependence with respect to V<sub>GS</sub> (as opposed to quadratic) so a reduced amount of current is delivered for a given control voltage

#### © Digital Integrated Circuits<sup>2nd</sup>

Devices

# Simple Model versus SPICE

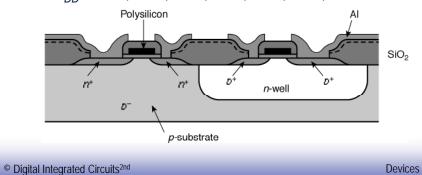

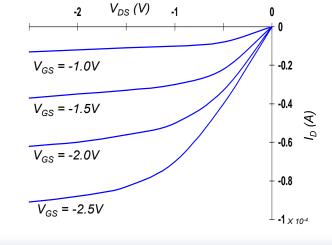

#### pMOS Equations

- - · change all n-tpye regions to p-type

- · change all p-type regions to n-type

- substrate is n-type (nWell)

- · channel charge is positive (holes) and (+)ve charged ions

- equations

© Digital Integrated Circuits<sup>2nd</sup>

- change  $V_{65}$  to  $V_{56}$  ( $V_{56}$  typically = VDD  $V_6$ )

- change  $V_{DS}$  to  $V_{SD}$  ( $V_{SD}$  typically = VDD  $V_{D}$ )

- change Vtn to |Vtp|

- pMOS threshold is negative, nearly same magnitude as nMOS

- other factors

- lower surface mobility, typical value,  $\mu_{p}$  = 220 cm<sup>2</sup>/V-sec

- body effect, change V<sub>SB</sub> to V<sub>BS</sub>

Devices

# Short Channel I-V Plot (PMOS)

All polarities of all voltages and currents are reversed

PMOS transistor, 0.25 $\mu$ , L<sub>d</sub> = 0.25 $\mu$ , W/L = 1.5, V<sub>DD</sub> = 2.5V, V<sub>T</sub> = -0.4V © Digital Integrated Circuits<sup>2nd</sup> Devices

# The MOS Current-Source Model

Determined by the voltages at the four terminals and a set of five device parameters

|      | V <sub>T0</sub> (V) | γ(V <sup>0.5</sup> ) | $V_{DSAT}(V)$ | k'(A/V²)               | λ(V-1) |

|------|---------------------|----------------------|---------------|------------------------|--------|

| NMOS | 0.43                | 0.4                  | 0.63          | 115 x 10⁻ <sup>6</sup> | 0.06   |

| PMOS | -0.4                | -0.4                 | -1            | -30 x 10⁻ <sup>6</sup> | -0.1   |

© Digital Integrated Circuits<sup>2nd</sup>

Devices

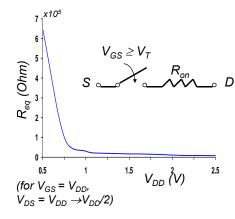

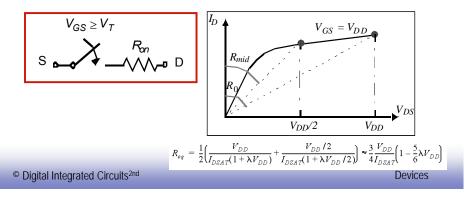

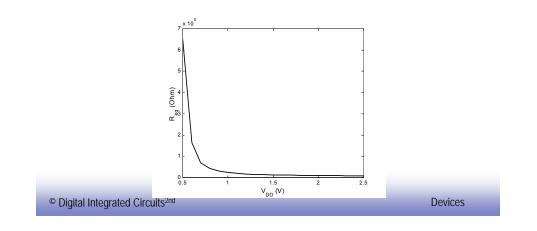

# The Transistor Modeled as a Switch

Modeled as a switch with infinite off resistance and a finite on resistance, Ron

- Resistance inversely proportional to W/L (doubling W halves R<sub>on</sub>)

- For  $V_{DD} >> V_T + V_{DSAT}/2$ ,  $R_{on}$ independent of V<sub>DD</sub>

- Once  $V_{DD}$  approaches  $V_{T}$ , *R*<sub>on</sub> increases dramatically

| V <sub>DD</sub> (V) | 1   | 1.5 | 2  | 2.5 |      |

|---------------------|-----|-----|----|-----|------|

| NMOS(kΩ)            | 35  | 19  | 15 | 13  | For  |

| PMOS (kΩ)           | 115 | 55  | 38 | 31  | divi |

(for W/L = 1) larger devices ide R<sub>ea</sub> by W/L

© Digital Integrated Circuits<sup>2nd</sup>

#### The Transistor as a Switch

• In digital VLSI, transistor is treated as a switch with infinite "off" resistance, and a finite "on" resistance *R*<sub>on</sub>.

• *R*<sub>on</sub> is time varying, nonlinear and dependent on transistor operating point. We can use the average value of resistances at the end points of the transition.

•  $R_{eq}$  is inversely proportional to (W/L) ratio of transistor. Doubling the transistor width cuts the resistance in half. (IDSAT is linear to (W/L))

# *MOS Capacitances Dynamic Behavior*

# The Transistor as a Switch

• For  $V_{DD}$ >> $V_T$ + $V_{DSAT}$ /2,  $R_{eq}$  is virtually independent of  $V_{DD}$ . On a minor increase on  $R_{eq}$  due to channel length modulation can be observed when raising  $V_{DD}$ .

• Once  $V_{DD} \rightarrow V_T$ ,  $R_{eq}$  increases dramatically.

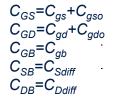

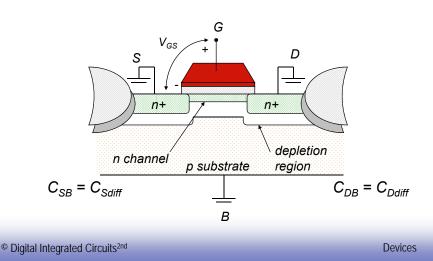

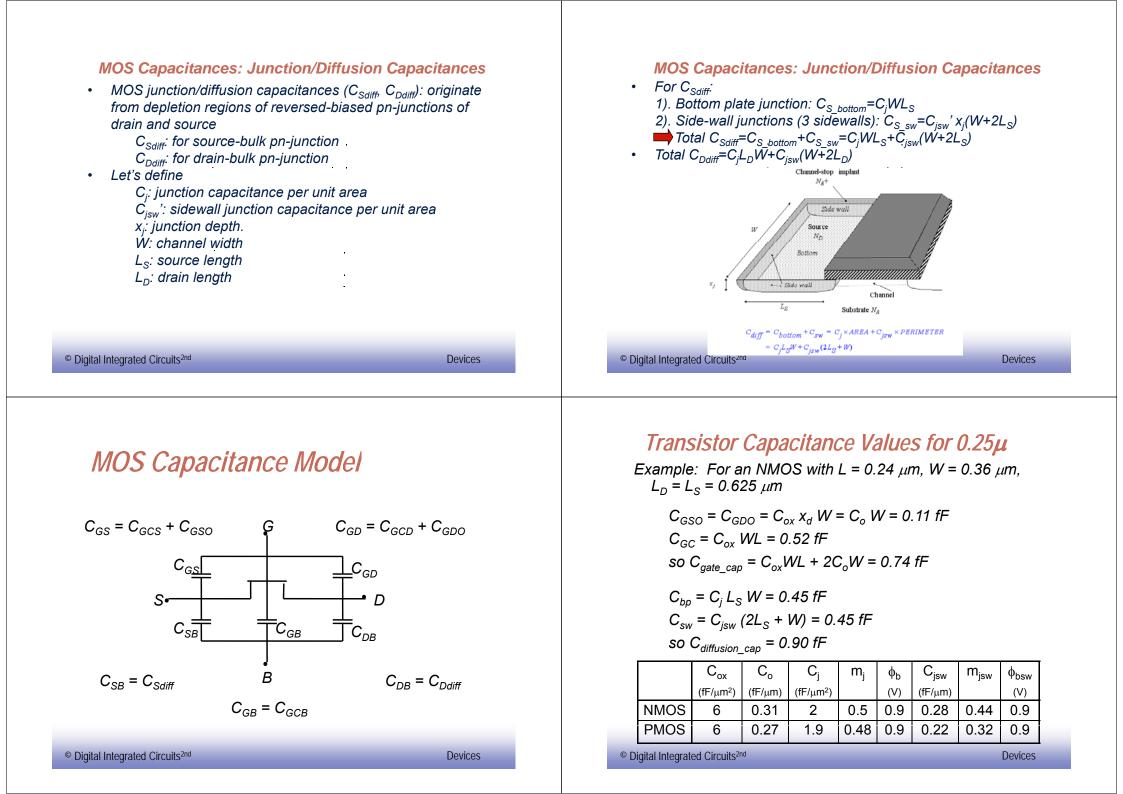

#### Capacitances of MOS Transistor

• MOS capacitances according to physical mechanisms Overlap capacitances:  $C_{gso}$ ,  $C_{gdo}$ Channel capacitances:  $C_{gs}$ ,  $C_{gd}$ ,  $C_{gb}$ Diffusion capacitance:  $C_{Sdiff}$ ,  $C_{Ddiff}$

• Lumped capacitance model of MOS transistor: capacitances between terminals without considering physical mechanisms

#### MOS Intrinsic Capacitances

- □ Structure capacitances

- □ Channel capacitances

© Digital Integrated Circuits<sup>2nd</sup>

Depletion regions of the reversebiased *pn*-junctions of the drain and source

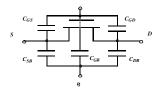

# MOS Structure Capacitances

#### MOS Capacitances: Structure Capacitances

MOS structure capacitance: Polysilicon gate originate from MOS structure 1). Gate capacitance  $C_a$  $C_{\alpha} = C_{\alpha x} W \cdot L$ , where  $C_{\alpha x} = \mathcal{E}_{\alpha x} / t_{\alpha x}$ Drain Source Lateral diffusion: during to n\* fabrication. both source and drain tends to extend somewhat below Gate bulk overla the oxide by  $x_{d}$ . (a) Top view Effective channel length:  $L_{eff} = L - 2x_d$ Gate oxide Gate capacitance considering x<sub>d</sub>: tox n\* n\*  $C_{a} = C_{ox} W \cdot L_{eff}$ 2). Overlap capacitance: C<sub>qso</sub>, C<sub>ado</sub> (b) Cross-section  $C_{aso} = C_{ado} = C_{ox} \cdot x_d \cdot W$ © Digital Integrated Circuits<sup>2nd</sup>

Devices

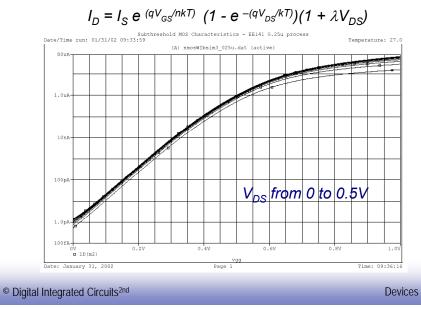

#### **Review:** Summary of MOS Operating Regions

- $\Box$  Cutoff (really subthreshold)  $V_{GS} \leq V_T$

- Exponential in  $V_{GS}$  with linear  $V_{DS}$  dependence

- $I_{D} = I_{S} \; e^{\;(qV_{GS}/nkT)} \; (1 e^{\;-(qV_{DS}/kT)}) \; (1 \lambda \; V_{DS}) \quad \text{where} \quad n \geq 1$

- □ Strong Inversion  $V_{GS} > V_T$

- Linear (Resistive)  $V_{DS} < V_{DSAT} = V_{GS} V_T$  $I_{D} = k' W/L [(V_{GS} - V_{T})V_{DS} - V_{DS}^{2}/2] (1 + \lambda V_{DS}) \kappa (V_{DS})$

- Saturated (Constant Current)  $V_{DS} \ge V_{DSAT} = V_{GS} V_T$  $I_{DSat} = k' W/L [(V_{GS} - V_T)V_{DSAT} - V_{DSAT}^2/2] (1 + \lambda V_{DS}) \kappa (V_{DSAT})$

|   |      | V <sub>T0</sub> (V) | γ(V <sup>0.5</sup> ) | V <sub>DSAT</sub> (V) | k'(A/V <sup>2</sup> )  | λ(V <sup>-1</sup> ) |

|---|------|---------------------|----------------------|-----------------------|------------------------|---------------------|

| Ī | NMOS | 0.43                | 0.4                  | 0.63                  | 115 x 10 <sup>-6</sup> | 0.06                |

| I | PMOS | -0.4                | -0.4                 | -1                    | -30 x 10 <sup>-6</sup> | -0.1                |

© Digital Integrated Circuits<sup>2nd</sup>

Devices

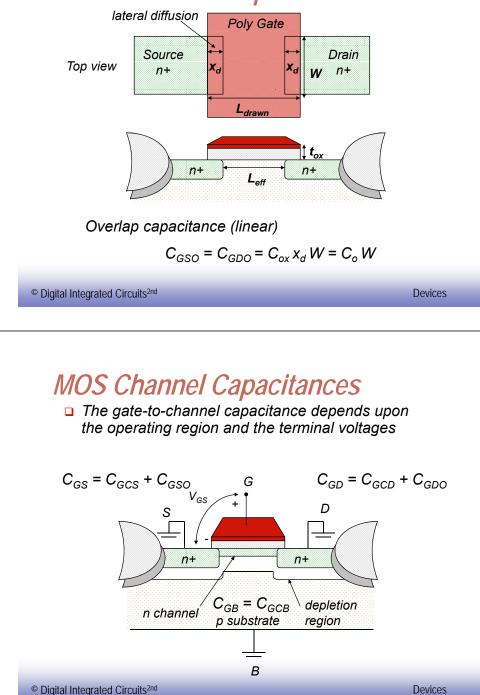

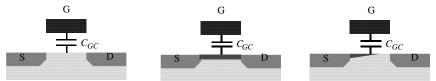

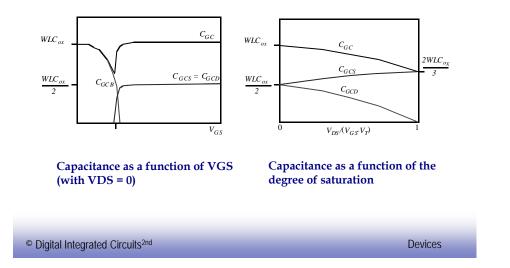

# Channel Capacitance

- MOS channel capacitances: originate from channel charge

- MOS gate-to-channel capacitances: Cab, Cas, Cad

- Distribution of gate capacitance among channel capacitances depends on operating conditions.

Cut-off

Saturation

#### Resistive MOS gate-to-channel capacitances in different operation regions

| Operation Region | $C_{gb}$                          | Cgs                   | Cgd                |

|------------------|-----------------------------------|-----------------------|--------------------|

| Cutoff           | C <sub>ox</sub> WL <sub>eff</sub> | 0                     | 0                  |

| Triode           | 0                                 | $C_{ox}WL_{eff}/2$    | $C_{ox}WL_{eff}/2$ |

| Saturation       | 0                                 | $(2/3)C_{ox}WL_{eff}$ | 0                  |

© Digital Integrated Circuits<sup>2nd</sup>

Devices

#### Average Distribution of Channel Capacitance

| Operation<br>Region | C <sub>GCB</sub>   | C <sub>GCS</sub>        | C <sub>GCD</sub>     | C <sub>GC</sub>         | C <sub>G</sub>                                 |

|---------------------|--------------------|-------------------------|----------------------|-------------------------|------------------------------------------------|

| Cutoff              | C <sub>ox</sub> WL | 0                       | 0                    | C <sub>ox</sub> WL      | C <sub>ox</sub> WL +<br>2C <sub>o</sub> W      |

| Resistive           | 0                  | C <sub>ox</sub> WL/2    | C <sub>ox</sub> WL/2 | C <sub>ox</sub> WL      | C <sub>ox</sub> WL +<br>2C <sub>o</sub> W      |

| Saturation          | 0                  | (2/3)C <sub>ox</sub> WL | 0                    | (2/3)C <sub>ox</sub> WL | (2/3)C <sub>ox</sub> WL +<br>2C <sub>o</sub> W |

- Channel capacitance components are nonlinear and vary with operating voltage

- Most important regions are cutoff and saturation since that is where the device spends most of its time

#### © Digital Integrated Circuits<sup>2nd</sup>

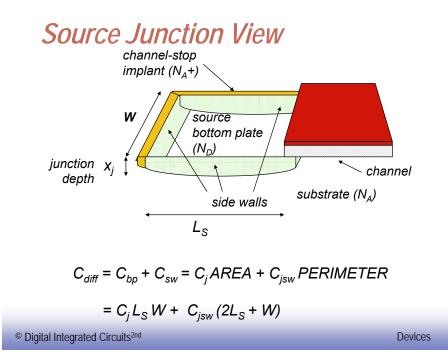

#### **MOS Diffusion Capacitances**

□ The junction (or diffusion) capacitance is from the reverse-biased source-body and drain-body pn-junctions.

#### Review: Reverse Bias Diode

□ All diodes in MOS digital circuits are reverse biased; the dynamic response of the diode is determined by depletion-region charge or junction capacitance

$C_i = C_{i0} / ((1 - V_D) / \phi_0)^m$

where  $C_{i0}$  is the capacitance under zero-bias conditions (a function of physical parameters),  $\phi_0$  is the built-in potential (a function of physical parameters and temperature)

and m is the grading coefficient

- $m = \frac{1}{2}$  for an abrupt junction (transition from n to pmaterial is instantaneous)

- m = 1/3 for a linear (or graded) junction (transition is gradual)

- Nonlinear dependence (that decreases with increasing) © Digital Integrated Circuits<sup>2nd</sup>

Devices

#### **Reverse-Bias Diode Junction Capacitance**

#### *Linearizing the Junction Capacitance*

Replace non-linear capacitance by large-signal equivalent linear capacitance which displaces equal charge over voltage swing of interest

$$C_{eq} = \frac{\Delta Q_j}{\Delta V_D} = \frac{Q_j(V_{high}) - Q_j(V_{low})}{V_{high} - V_{low}} = K_{eq}C_{j0}$$

$$K_{eq} = \frac{-\phi_0^m}{(V_{high} - V_{low})(1-m)} [(\phi_0 - V_{high})^{1-m} - (\phi_0 - V_{low})^{1-m}]$$

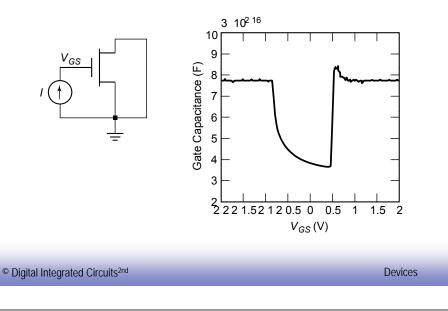

# Gate Capacitance

# Measuring the Gate Cap

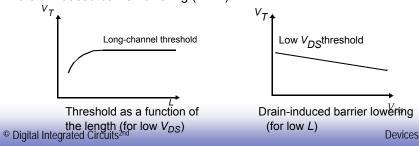

#### Other (Submicon) MOS Transistor Concerns

- Velocity saturation

- Subthreshold conduction

- Transistor is already partially conducting for voltages below  $V_{\rm T}$

- Threshold variations

- In long-channel devices, the threshold is a function of the length (for low V<sub>DS</sub>)

- In short-channel devices, there is a drain-induced threshold barrier lowering at the upper end of the V<sub>DS</sub> range (for low L)

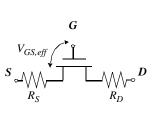

- Parasitic resistances

resistances associated with the source and drain contacts

```

Latch-up

© Digital Integrated Circuits<sup>2nd</sup>

```

Devices

# Threshold Variations

• For short-channel transistors:

✓ The depletion regions of source and reverse-biased drain junction, previously was ignored in long-channel device. But for short-channel device, they become relatively more important with shrinking channel length. Since a part of the region below gate is already depleted, a smaller VT suffices to cause strong inversion. Thus, VTO decreased with L for short-channel device.

✓ Raising drain-source (bulk) voltage also increases the width of drainjunction depletion region, hence VTO decreases with increasing VDS: drain-induced barrier lowering (DIBL).

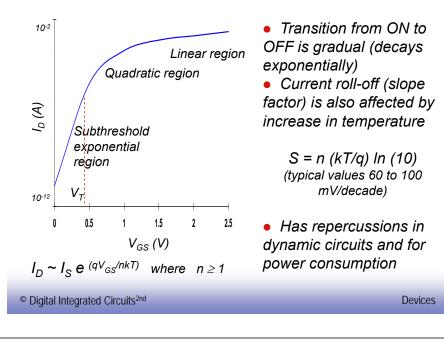

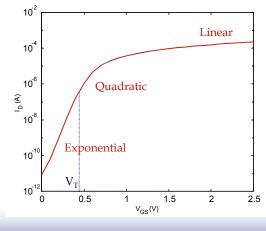

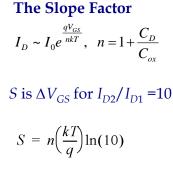

# Subthreshold Conductance

# Sub-Threshold Conduction

Typical values for S: 60 .. 100 mV/decade

© Digital Integrated Circuits<sup>2nd</sup>

Devices

# Subthreshold I<sub>D</sub> vs V<sub>GS</sub>

#### Subthreshold $I_D$ vs $V_{DS}$ $I_D = I_S e^{(qV_{GS}'^{nkT})} (1 - e^{-(qV_{DS}'^{kT})})(1 + \lambda V_{DS})$

# Summary of MOSFET Operating Regions

#### $\Box$ Strong Inversion $V_{GS} > V_T$

- Linear (Resistive)  $V_{DS} < V_{DSAT}$

- Saturated (Constant Current)  $V_{DS} \ge V_{DSAT}$

- $\Box$  Weak Inversion (Sub-Threshold)  $V_{GS} \leq V_T$

- Exponential in V<sub>GS</sub> with linear V<sub>DS</sub> dependence

Devices

#### Parasitic Resistances

| © Digital | Integrated | Circuits <sup>2nd</sup> |

|-----------|------------|-------------------------|

|           |            |                         |

#### Latch-Up

- Latch-up is a very real, very important factor in circuit design that must be accounted for

- Due to (relatively) large current in substrate or n-well

- create voltage drops across the resistive substrate/well

- most common during large power/ground current spikes

- turns on parasitic BJT devices, effectively shorting power & ground

often results in device failure with fused-open wire bonds or interconnects

- hot carrier effects can also result in latch-up

- latch-up very important for short channel devices

- Avoid latch-up by

© Digital Integrated Circuits<sup>2nd</sup>

- including as many substrate/well contacts as possible

- rule of thumb: one "plug" each time a tx connects to the power rail

limiting the maximum supply current on the chip

- Infining the maximum supply current on the chip

# **SPICE MODELS**

#### Level 1: Long Channel Equations - Very Simple

- Level 2: Physical Model Includes Velocity Saturation and Threshold Variations

- Level 3: Semi-Emperical Based on curve fitting to measured devices

- Level 4 (BSIM): Emperical Simple and Popular

#### MAIN MOS SPICE PARAMETERS

| Parameter Name                                  | Symbol | SPICE<br>Name | Units     | Default<br>Value |

|-------------------------------------------------|--------|---------------|-----------|------------------|

| SPICE Model Index                               |        | LEVEL         | -         | 1                |

| Zero-Bias Threshold Voltage                     | VTO    | VTO           | v         | 0                |

| Process Transconductance                        | k'     | КР            | A/V2      | 2.E-5            |

| Body-Bias Parameter                             | g      | GAMMA         | V0.5      | 0                |

| Channel Modulation                              | 1      | LAMBDA        | 1/V       | 0                |

| Oxide Thickness                                 | tox    | T OX          | m         | 1.0E-7           |

| Lateral Diffusion                               | xd     | LD            | m         | 0                |

| Metallurgical Junction Depth                    | xj     | ХJ            | m         | 0                |

| Surface Inversion Potential                     | 2 fF   | PHI           | v         | 0.6              |

| Substrate Doping                                | NA,ND  | NSUB          | cm-3      | 0                |

| Surface State Density                           | Qss/q  | NSS           | cm-3      | 0                |

| Fast Surface State Density                      |        | NF S          | cm-3      | 0                |

| Total Channel Charge Coefficient                |        | NEFF          | -         | 1                |

| Type of Gate Material                           |        | TPG           | -         | 1                |

| Surface Mobility                                | m0     | UO            | cm2/V-sec | 600              |

| Maximum Drift Velocity                          | umax   | VMAX          | m/s       | 0                |

| Mobility Critical Field                         | xcrit  | UCRIT         | V/cm      | 1.0E4            |

| Critical Field Exponent in Mobility Degradation |        | UEXP          | -         | 0                |

| Transverse Field Exponent (mobility)            |        | UTRA          | -         | 0                |

© Digital Integrated Circuits<sup>2nd</sup>

Devices

#### SPICE Parameters for Parasitics

| Parameter Name                           | Symbol            | SPICE<br>Name | Units            | Default<br>Value |

|------------------------------------------|-------------------|---------------|------------------|------------------|

| Source resistance                        | R <sub>S</sub>    | RS            | Ω                | 0                |

| Drain resistance                         | R <sub>D</sub>    | RD            | Ω                | 0                |

| Sheet resistance (Source/Drain)          | R <sub>o</sub>    | R SH          | വ⁄ം              | 0                |

| Zero Bias Bulk Junction Cap              | $C_{j\theta}$     | CJ            | F/m <sup>2</sup> | 0                |

| Bulk Junction Grading Coeff.             | m                 | МJ            | -                | 0.5              |

| Zero Bias Side Wall Junction Cap         | C <sub>jsw0</sub> | CJSW          | F/m              | 0                |

| Side Wall Grading Coeff.                 | m <sub>sw</sub>   | MJSW          | -                | 0.3              |

| Gate-Bulk Overlap Capacitance            | CgbO              | CGBO          | F/m              | 0                |

| Gate-Source Overlap Capacitance          | C <sub>gsO</sub>  | CGSO          | F/m              | 0                |

| Gate-Drain Overlap Capacitance           | CgdO              | CGDO          | F/m              | 0                |

| Bulk Junction Leakage Current            | IS                | IS            | A                | 0                |

| Bulk Junction Leakage Current<br>Density | J <sub>S</sub>    | JS            | A/m <sup>2</sup> | 1E-8             |

| Bulk Junction Potential                  | ¢o                | РВ            | v                | 0.8              |

#### © Digital Integrated Circuits<sup>2nd</sup>

Devices

#### SPICE Transistors Parameters

| Parameter Name                     | Symbol | SPICE Name | Units | Default<br>Value |

|------------------------------------|--------|------------|-------|------------------|

| Drawn Length                       | L      | L          | m     | -                |

| Effective Width                    | W      | W          | m     | -                |

| Source Area                        | AREA   | AS         | m2    | 0                |

| Drain Area                         | AREA   | AD         | m2    | 0                |

| Source Perimeter                   | PERIM  | PS         | m     | 0                |

| Drain Perimeter                    | PERIM  | PD         | m     | 0                |

| <b>Squares of Source Diffusion</b> |        | NRS        | -     | 1                |

| <b>Squares of Drain Diffusion</b>  |        | NRD        | -     | 1                |